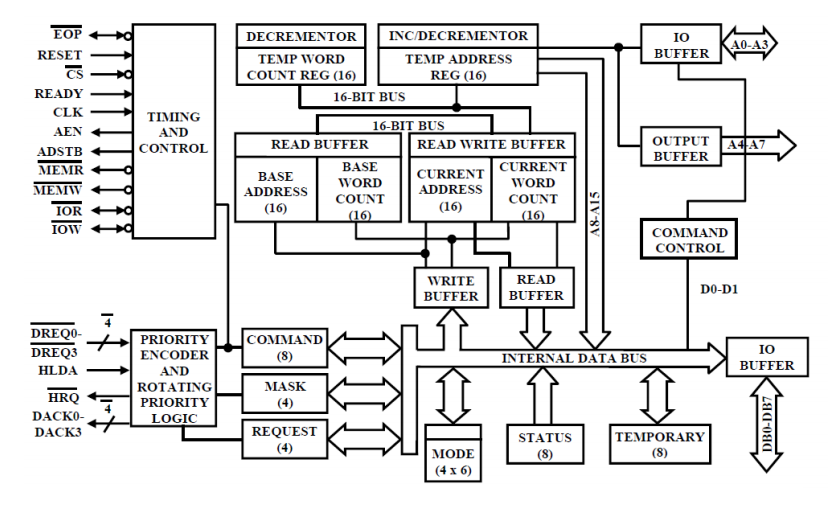

Block Diagram of 8237

8237 Internal Registers

- The

current address registerholds a 16-bit memory address used for the DMA transfer. - each channel has its own current address register for this purpose.

- When a byte of data is transferred during a DMA operation, CAR is either incremented or decremented. depending on how it is programmed

- The current word count register programs a channel for the number of bytes to transferred during a DMA action.

- The

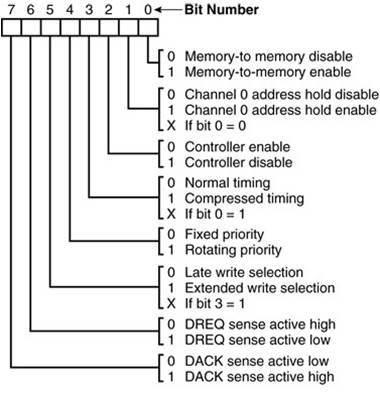

command registerprograms the operation of the 8237 DMA controller. - The register uses bit position 0 to select the memory-to-memory DMA transfer mode.

- Memory-to-memory DMA transfers use DMA channel

- DMA channel 0 to hold the source address

- DMA channel 1 holds the destination address

The base address(BA) andbase word count(BWC) registers are used when auto-initialization is selected for a channel.- In auto-initialization mode, these registers are used to reload the CAR and CWCR after the DMA action is completed.

- The

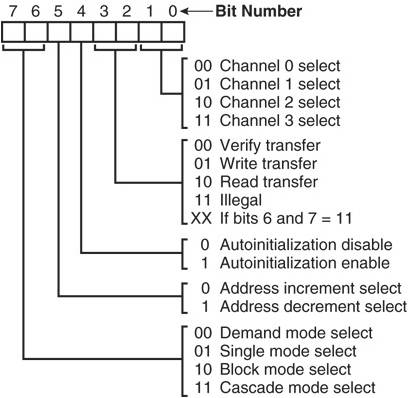

mode registerprograms the mode of operation for a channel. - Each channel has its own mode register as selected by bit positions 1 and 0.

- Remaining bits of the mode register select operation, auto-initialization, increment/decrement, and mode for the channel

- The

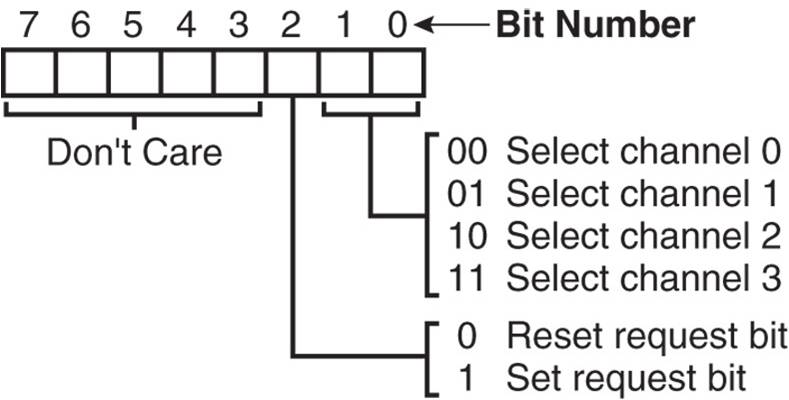

bus request registeris used to request a DMA transfer via software.- very useful in memory-to-memory transfers, where an external signal is not available to begin the DMA transfer

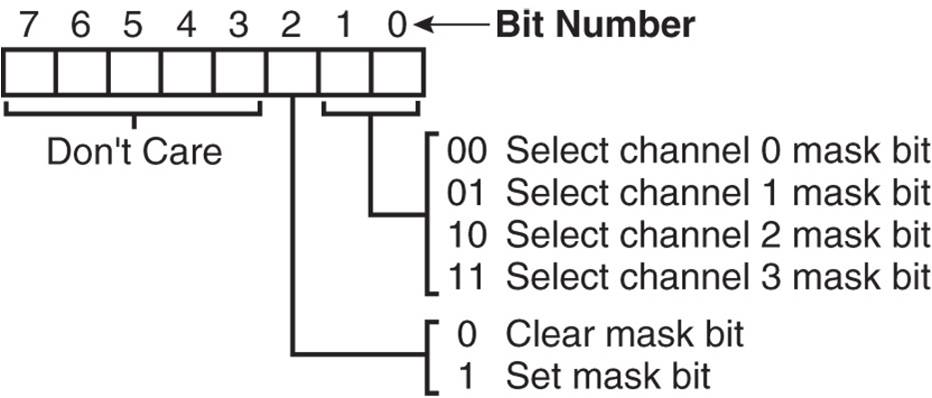

- The

mask register set/resetsets or clears the channel mask.- if the mask is set, the channel is disabled

- the RESET signal sets all channel masks to disable them

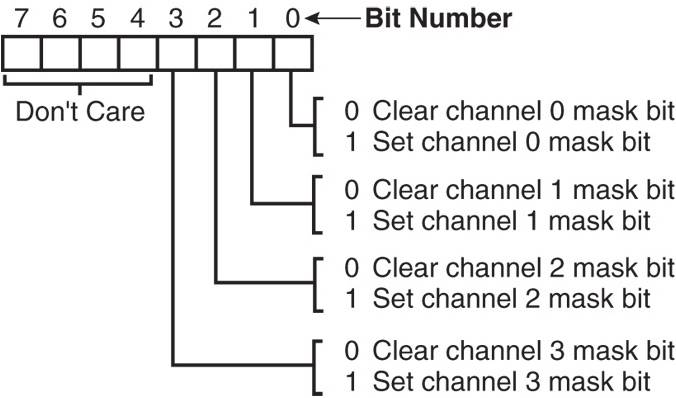

- The

mask registerclears or sets all of the masks with one command instead of individual channels, as with the MRSR. - The

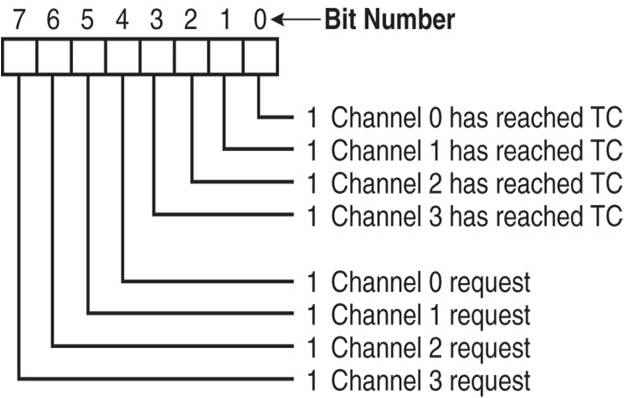

status registershows status of each DMA channel. The TC bits indicate if the channel has reached its terminal count (transferred all its bytes). - When the terminal count is reached, the DMA transfer is terminated for most modes of operation.

- The request bits indicate whether the DREQ input for a given channel is active.

CAR

CWCR

CR

BA and BWC

MR

BR

MRSR

MSR

SR

8237 Software Commands

Master clear

Acts exactly the same as the RESET signal to the 8237. As with the RESET signal, this command disables all channels

Clear mask register

Enables all four DMA channels.

Clear the first/last flip-flop

Clears the first/last (F/L) flip-flop within 8237. The F/L flip-flop selects which byte (low or high order) is read/written in the current address and current count registers. if F/L = 0, the low-order byte is selected if F/L = 1, the high-order byte is selected Any read or write to the address or count register automatically toggles the F/L flip-flop.